# **Development Status of MPS for the IFMIF/EVEDA Accelerator (2)**

Takahiro Narita \*, Toshiyuki Kojima, Kazuyoshi Tsutsumi, Hiroki Takahashi, Hironao Sakaki Japan Atomic Energy Agency (JAEA), Rokkasho, Aomori, JAPAN

### Abstract

International Fusion Materials Irradiation Facility (IFMIF) is an accelerator-based neutron irradiation facility to develop materials for a demonstration fusion reactor next to ITER. For providing materials to make a decision of IFMIF construction, Engineering Validation and Engineering Design Activities (EVEDA) under the Broader Approach agreement have been started. IFMIF/EVEDA prototype accelerator consists of Injector, a 175MHz RFQ linac, a matching section, the first section of Superconducting RF linac, a high energy beam transport line and a beam dump, and the acceleration tests by employing the deuteron beam of 125mA are planning in Rokkasho, Aomori, Japan. One of the control system for Linear IFMIF Prototype Accelerator (LIPAc), Machine Protection System (MPS) realize the beam rapid stop to minimize the beam loss. This paper presents the development status of the MPS, and the prospects to apply them to the Injector test.

# IFMIF/EVEDA 加速器制御系機器保護システム(MPS)の開発状況 (2)

## 1. はじめに

国際核融合材料照射施設(IFMIF)に関する工学 実証及び工学設計活動(EVEDA)におけるプロト タイプ加速器(Linear IFMIF Prototype Accelerator: LIPAc)は、9MeV/125mA の大強度CW D+ビーム を生成する。LIPAc の制御システムは、中央制御シ ステム(CCS)、ローカルエリアネットワーク (LAN)、人員保護システム(PPS)、機器保護シ ステム(MPS)、タイミングシステム(TS)、ロー カル制御システム(LCS)の6サブシステムによっ て構成される<sup>[2]</sup>。そして欧州が LCS を、日本がその 他5サブシステムを担当し、日欧共同で制御システムの開発を進めている。

本件では MPS の開発状況として、入射器の"インターフェース (I/F) 部"について詳細に報告する。

# 2. MPS の構成

LIPAc の MPS は

- ✓ ビーム停止所要時間を 10µS 以下とする

- ✓ 効率的な運転再開シーケンスを実装する

- ✓ 実績のある機器をベースにし、確実で堅牢な システムを構築する

- ✓ 機器・開発環境を統一する

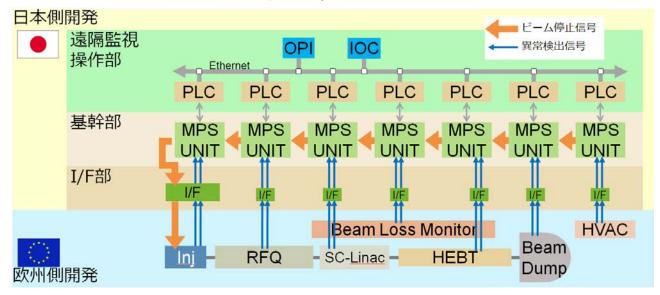

を方針として開発を進めている。MPS 構成概略を図1 に示す。MPS は PLC 及び IOC からなる "遠隔監視操作部"、インタロック信号の高速転送を担う "基幹部"、高速瞬時停止と効率的起動シーケンスを実施する"インターフェース (I/F) 部 "の 3 層構成である。

図 1: MPS のシステム構成

<sup>#</sup> narita.takahiro@jaea.go.jp

"遠隔監視操作部"は、"基幹部 "や" I/F 部 "で取り扱う物理的電気信号を EPICS ヘインテグレートする CCS とのインターフェース機能を有する。

"基幹部"は、運用実績のあるインタロックユニットで構成され、MPS の根幹となるインタロック信号を高速転送するという最重要かつクリティカルな機能を有する。

"I/F 部"は、欧州各国で開発される加速器各機器と基幹部とを柔軟に接続する緩衝機能を有する。 また、高速にビーム停止させるだけでなく、効率良 く運転再開させる為の信号処理を行う機能も有する。

## 3. 開発状況

MPS は加速器構成機器との取り合いが重要であるため、欧州各国が開発する各機器の設計・製作の進捗に合わせて開発を進めている。入射器の日本への搬入が 2013 年 3 月となり、入射器仕様はほぼ確定されたことから、入射器ビーム停止方式、MPS ビーム停止要求及びビーム停止許容時間についての検討を日欧共同で実施している。

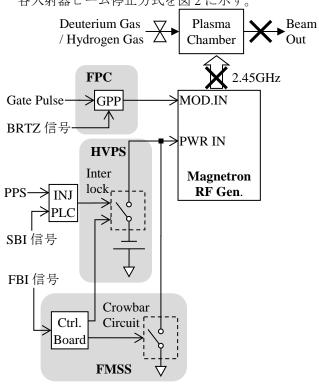

### 3.1 入射器ビーム停止機構の検討

入射器のビーム停止は「プラズマチェンバーへの2.45GHz 供給遮断」により行われる。入射器にビーム停止信号を出力する MPS の入射器 L/F 部においては "高速ビーム停止"だけでなく、"短時間のビーム停止"が特に求められる。そこでビーム停止要求の原因によって"Fast Beam inhibition (FBI)"、"Slow Beam inhibition (SBI)"、"Beam Reset to Zero (BRTZ)"の異なる 3 種類の停止方法を実現することとした。

#### 3.1.1 FBI 機構

FBI 機構は、高速ビーム停止を主目的とした停止 方法であり、ビーム停止時間  $20 \mu$  秒以内を目標とする。MPS ビーム停止要求信号(FBI 信号)が入射器の Fast Magnetron Shutdown System(FMSS)に入力される と FMSS がイオン化用 RF 高圧電源印加を Crowbar Circuit によって瞬時に停止する。これによりプラズ マチェンバーでのプラズマ生成を阻害しビームが停止される。

### 3.1.2 SBI 機構

SBI 機構は、高速かつ確実なビーム停止を目的としており、100m 秒以内のビーム停止を実現する。MPS ビーム停止要求信号(SBI 信号)が、入射器サブシステムの Magnetron Power Supply Interlock 機能を持つ PLC へ転送され、PLC がイオン化用 RF 高圧電源印加を停止されることでビームが停止される。確実なビーム停止を実現するため PPS からのビーム停止信号もこの機構に入力される。

## 3.1.3 BRTZ 機構

BRTZ 機構は、高速かつ短時間のビーム停止(短時間ビーム停止後、すぐにビーム復帰)を実現する。

ビーム停止時間は  $50\mu$  秋以内を目標とし、ビーム停止後 1 周期のみのビーム停止(1 ビーム周期でのビーム復帰)を可能とする。これは入射器に入力されるタイミング信号の Gate Pulse をビーム停止信号受信時のみ遮断することにより実現が可能である。

各入射器ビーム停止方式を図2に示す。

図2:入射器ビーム停止方式

## 3.2 MPS ビーム停止要求信号の検討

3 種類のビーム停止機構実現のため、各停止機構のビーム停止要求信号とロジックについて検討を行った結果、信号集約とラッチ設定は基幹部の MPS モジュールによって実現できる見通しが得られた。

FBI 機構、SBI 機構については、最終的に集約し ラッチされたビーム停止要求信号をそれぞれ FMSS、 入射器 PLC へ出力することが要求されるが、これは 基幹部に使用される MPS ユニットで実現可能であ ることを確認した。

しかしながら BRTZ 機構においては、最終的に集約されたラッチされないビーム停止要求信号により入射器のタイミング信号を制御することが要求されるため、基幹部 MPS ユニットでは実現不可能である。そこで、基幹部と入射器との"I/F 部"を開発し、BTRZ 機構を実現することとした。

### 3.2.1 Fast Procedure Circuit

BRTZ機構は、基幹部と入射器との"I/F 部"としてFast Procedure Circuit(FPC)を開発し実現する。FPCには、LIPAc 運転などの検討により、今後、機能追加の要求が想定される。そのため、高速処理性能とロジック改良の簡易性から、FPC の論理回路にはFPGA を使用することとした。

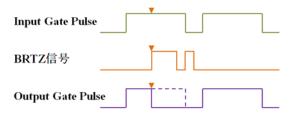

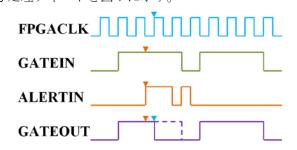

BRTZ 機構の機能詳細は、①ビーム停止要求時にはイオン化用 RF ジェネレータの Magnetron Modulation Input へ入力される Gate Pulse 信号を速やかに無効化する、②ビーム停止要求解除時には Gate Pulse 信号に同期し次のパルスエッジから Gate Pulse 信号の無効化を解除する、の 2 点である。これをファンクションチャートに変換したものを図 3 に示す。

図3:GPPファンクションチャート

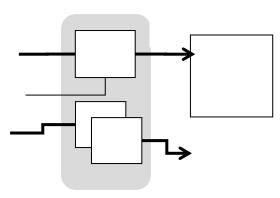

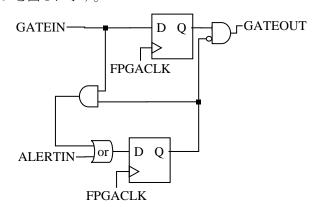

このビーム停止要求信号(BRTZ 信号)によりゲートパルス信号を制御する機能を Gate Pulse Processor(GPP)機能とし、FPC 機能の一つとして搭載する。FPC内部ブロックを図4に示す。

図 4: FPC 内部ブロック図

## 4. 構成機器(FPC)の開発状況

## 4.1 FPC 設計·製作

開発初期段階であり、また開発した FPC を EU にて試験する予定であることから、FPC テストモジュールを製作することとした。

図 5: FPC 外観

テストモジュールは小型アルミケース (W240D150H80)に収め、電源は AC アダプターとし 可搬性を高めた。FPC 外観を図 5 に示す。

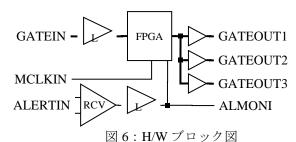

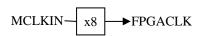

内部回路は、主に1ボード Xilinx フラッシュ内蔵 FPGA(3.3vI/O=100,max.324MHz,単一5V 電源)で構成され、開発初期段階での設計変更に迅速・柔軟に対応可能である。Gate Out ポートは TTL レベルではなく、MOSFET により  $50\Omega$  負荷を 0.5V ドライブし、3 出力とした。ハードウェアブロックを図 6 に、また入出力端子リストを表 2 に示す。

表 2: 入出力端子リスト-1

| Pin Name         | Dir. | Signal                             |                                         |

|------------------|------|------------------------------------|-----------------------------------------|

| GATEIN           | IN   | SMA-J Single end $Zi=50 \Omega$    | min0.6V<br>max.+7.8V                    |

| GATEOUT[31]      | OUT  | SMA-J 5V Single end Zo= $50\Omega$ | min120mA<br>max.+ 120mA<br>10Vmax@Open  |

| MCLKIN           | IN   | SMA-J Single end $Zi=50 \Omega$    | DC Bias=1.65V                           |

| ALERTIN<br>(P-S) | IN   | M3 Screw<br>Terminal<br>Diff.      | min2.7V<br>max.+2.7V<br>$Zi=120 \Omega$ |

| ALMONI           | OUT  | SMA-J<br>Single end                | LVTTL                                   |

| PWR-IN           | IN   | DC-Jack<br>PWR.Supply              | min.18V<br>max.36V                      |

図3のGPPファンクションチャートに対し、96MHzクロック動作を適用し同期化する。GPP信号処理チャートを図7に示す。

図 7: GPP 信号処理チャート

上記の GPP 信号処理チャートからロジック設計を行い、論理回路を FPGA に生成した。論理ブロックを図8に示す。

図 8: GPP 論理ブロック図

## 4.2 動作確認試験

### 4.2.1 テストベンチ

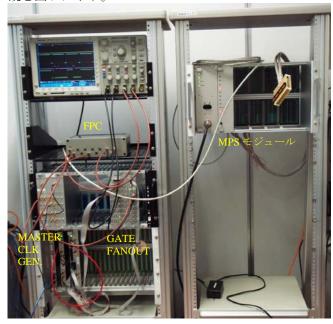

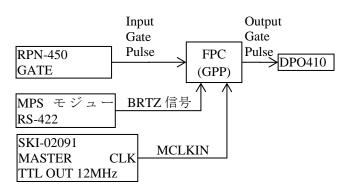

FPC テストモジュールの動作特性の確認試験を、 実使用環境のタイミングシステムと接続したテスト ベンチを構築して行った。接続したテストベンチ外 観を図9に示す。

図9: テストベンチ外観

ビーム停止信号は MPS モジュール差動伝送出力信号(RS-422)を、Gate Pulse信号にはタイミングシステム GATE FANOUT(RPN-450)を、MCLK 信号にはMASTER CLK GEN. TTL OUT 12MHz(SKI-02091)を使用した。結線を図 10 に示す。

図 10: テストベンチ結線図

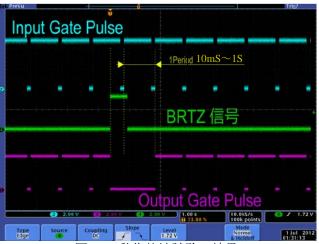

### 4.2.2 動作特性

GPP 動作確認の結果、ALERTIN に入力された信号に対して、10.4n 秒後にロジック出力処理され、

図11:動作特性試験の結果1

GATEIN に入力された Gate Pulse 信号期間に同期して問題無く信号処理されていた。

図 12:動作特性試験の結果 2

また機器(FPC)としての遅延合計時間は、40n 秒未満(入出力段デバイス遅延、ロジック遅延)であった。動作特性試験結果の代表例を図11、図12に示す。

## 5. まとめ

MPS に関するビーム停止方式と入射器サブシステムとの具体的なインターフェース仕様が策定され、システム検討を実施し、システム構成機器の開発を進めている。

ゲートパルス処理機能を搭載した FPC により、BRTZ 機構実現の目途を得た。FPC の信号伝搬遅延は 40nS 未満 (許容伝搬遅延比 0.4%未満)を実現した。今後、開発した入射器 I/F モジュールの状態表示灯などの調整を行った後、EU において本試作機を用いた入射器との接続試験を実施し、ビーム停止機構の検証を行う(2012 年秋)。

また次ステップとして、MPS と EU 側各加速器サブシステムとのインターフェース仕様の検討を進め、順次必要な I/F 部の開発、改良を行う予定である。また、入射器以外の加速器サブシステムにおいても、EU にて MPS I/F 部の接続試験を実施する計画である。

## 参考文献

- [1] S. Maebara "DESIGN OF AN RF INPUT COUPLER FOR THE IFMIF/EVEDA RFQ LINAC" Proceedings of IPAC'10, Kyoto, Japan

- [2] H.Takahashi, et al., "OVERVIEW OF THE CONTROL SYSTEM FOR THE IFMIF/EVEDA ACCELERATOR" Proceedings of Particle Accelerator Society Meeting 2009, JAEA, Tokai, Naka-gun, Ibaraki, Japan