# SRILAC 用マシンプロテクションシステムの構築 DEVELOPMENT OF MACHINE PROTECTION SYSTEM FOR SRILAC

内山暁仁<sup>#, A)</sup>, 込山美咲 A), 藤巻正樹 A), 熊谷桂子 A), 山内啓資 B), 金子健太 B)

Akito Uchiyama <sup>#, A)</sup>, Misaki Komiyama A), Masaki Fujimaki A), Keiko Kumagai A),

Hiromoto Yamauchi B), Kenta Kaneko B)

A) RIKEN Nishina Canter

B) SHI Accelerator Service Ltd.

## Abstract

The RIKEN linear accelerator (RILAC) is implemented as one of the injectors of RIBF at RIKEN Nishina Center. A superconducting RILAC (SRILAC) has been installed to search for superheavy elements of 119 and higher. In the past, the machine protection system for RILAC was constructed by a combination of simple relay circuits. On the other hand, most of the other parts of the RIBF have been equipped with machine protection systems using MELSEC-Q series since 2006. Since the beam intensity has been increased and to prevent breakdown of the superconducting cavity due to beam orbit changes by such as a trouble of power supplies, the SRILAC project requires enhanced machine protection system. For this reason, we have realized the BIS with higher response performance than the conventional system by using the FA-M3 base. Additionally, FPGA modules have been introduced to achieve response performance faster than 1 msec in FA-M3 based system. The BIS for SRILAC has been implemented and the beam commissioning has been successfully completed in 2020.

# 1. はじめに

理研 RIBF の入射器の一つとして線形加速器 RILAC が実装されている。RILAC は RIBF の入射器としてだけ でなく、それ単独での実験にもビームを提供しており SRILAC プロジェクトによって現在 119 番以上の超重元 素探索実験が進行中である。SRILAC プロジェクトにお ける主要なアップグレードは次の二点である。一つ目は 新たに28 GHz 超電導 ECR イオン源を上流にインストー ルし、ビーム強度を増強した事である[1]。次にビームエ ネルギー増強を目的として既存RILACキャビティの下流 に超伝導リニアック(SRILAC)を実装した事である[2]。 アップグレードによってビーム強度とエネルギーが増強さ れた結果、加速器コンポーネントの故障が引き起こす意 図しないビーム軌道の変化が実験装置や SRILAC 下流 の RIBF ビームラインにトラブルを及ぼす可能性も高く なった。また超電導キャビティのトラブル、例えばビーム ロスによる真空悪化でクエンチさせてしまう、といった事 態は防がなければならない。したがって、ビームからハー ドウェアを保護するための仕組みである、マシンプロテク ションシステムは従来に比べ高い性能を持つ必要がある。 上記を目的として SRILAC 運転にむけシステムの開発を 行った。

## 2. システム基本設計

## 2.1 従来システム

SRILAC プロジェクト以前の RILAC におけるインターロックシステムは、メカニカルリレーを組み合わせたハードウェアのみで実現されていた。したがって従来システムの汎用性は高くなく、入力信号の増加やロジックの変更

# a-uchi@riken.jp

によりハードウェアの回路修正が必要であった。またキャビティの放電、真空ゲートバルブの閉ステータス等の入力信号で異常を判断するマシンプロテクションと、放射線管理区域への入退扉の開閉ステータスによってビーム停止させるヒューマンプロテクションの双方が、同じシステムで運用されていた事が、配線やロジックを複雑化させる要因にもなっていた。

#### 2.2 Beam Interlock System

RILAC 以外の RIBF 加速器施設では 2006 年より Programmable Logic Controller (PLC)である MELSEC-Q シリーズを用いたマシンプロテクションシステムとして Beam Interlock System (BIS) が導入された[3]。BIS は入力された電磁石電源の異常信号、バッフルスリットの電流値等から、予め定められたシーケンスのもとにビームチョッパーとファラデーカップを挿入することで速やかにビーム停止させるシステムである。RIBF 加速器施設における BIS (RIBF BIS) はそれぞれに CPU がインストールされた 5 つのステーションにて構成されており、各々のステーションが MELSECNET/H のループ構成で接続されてPU 間通信を行っている。デジタル/アナログ入力約 400 点を異常信号としてトリガにして 10 msec オーダーの応答速度でビーム停止することが可能である。

#### 2.3 検討

SRILAC プロジェクトでのマシンプロテクションシステムの開発にあたり、考慮事項[4]を洗い出し以下の通り検討を行った。

- ハードウェア、ソフトウェア共、できるだけ複雑化を 避ける。

- ヒューマンプロテクションとマシンプロテクションは明確にシステムを分離する。

- システムロジックの主要部分は RIBF BIS を踏襲す

ろ

- 長期的なメンテナンスが可能なハードウェアの選択をする。

- システム改修や迅速なトラブル対応を可能とするため、システム開発、運用の工程は全てチーム内で 完結する。

- 上位システムは RIBF での制御標準プロトコルである EPICS Channel Access (CA) をベースに開発を行う。

- 超伝導キャビティへのマシンプロテクションは一般 的な PLC で実現できる応答性能より高い性能を実 現する。

- 急なインターロック信号の取り込みのリクエストに対しても対応可能な拡張性を持たせる。

## 3. SRILAC BIS 仕様

### 3.1 コントローラ

ハードウェアの選定において、チーム内で開発、運用を完結し、長期的なメンテナンスが実現可能なシステムを検討した結果、RIBFで多くの実績[5-7]があり、扱い慣れている FA-M3 シリーズの PLC によって SRILAC 用BIS (SRILAC BIS)のシステム構築をすることにした。プロトタイプで内部レジスタの上限数に問題が出る可能性があった事から、シーケンス CPU モジュールはシステム構築当時一番高性能であった F3SP76-7S を採用した。F3SP76-7S 上に BIS の主要シーケンスが実装された一方で、ユーザインターフェースといった上位システムをEPICS で実現する手段として、Linux CPU であるF3RP71[8]もインストールされ、マルチ CPU 構成になっている。

#### 3.2 通信

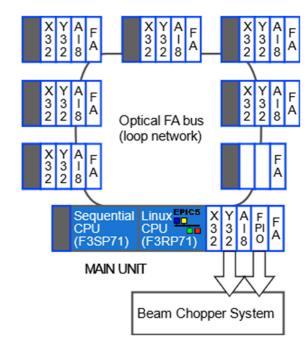

シーケンス CPU モジュールが実装されたステーションが FL-net で CPU 間通信するシステム[9]を構築した結果、最小構成(2台)でも通信に起因する遅延が数 msec あり、I/O 数の増加によって、さらに遅延が大きくなる事がわかった。よって SRILAC BIS では CPU 間通信の使用は避け、CPU モジュールがインストールされたメインユニットが 7台のサブユニットと光 FA バスで通信する構成にした。FA バスで通信することで、FA-M3シリーズ間相互の情報交換ができ、リモートI/Oシステムを構築することができる。本システムでは、光ファイバーを用いたループ構成で冗長化し、FA バスネットワークを構築した(Fig. 1参照)。ケーブル長、入力点数をもとに本構成で FA リンクに起因した I/O リフレッシュ時間を計算したところ、理論上約 110 μsec である。

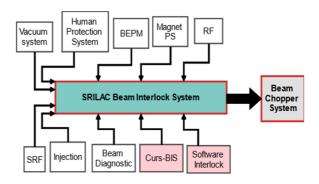

## 3.3 シーケンス

SRILAC 運転におけるマシンプロテクションは、SRILAC BIS がビームチョッパースイッチへ出力する中心部分として構成され、各システムが出力したインターロック信号をSRILAC BIS に入力して実現している(Fig. 2 参照)。BIS への各入力信号に対し有効/無効の設定、トリガレベルの設定、ホールドの設定をオペレータが運転に応じて行い、異常判定時にはチョッパーでビーム停止するのと同時に、設定されたファラデーカップを挿入

する、といったシンプルなシーケンスになっている。

#### 3.4 標準 I/O

FA-M3 シリーズで標準的に使用されている入力モジュール(標準 I/O)である F3XD32-3F[10]を採用した。またビームチョッパーを駆動させる出力モジュールとして、カタログスペックで応答速度 0.1 msec 以下の F3YD32-1H[10]を使用、ファラデーカップを駆動させる出力に関しては速い応答時間は必要ないので、応答速度 1 msec 以下の F3YD32-1P[10]を採用している。PLC ユニットと入出力点数に関して、Table 1 に示す。

Figure 1: System chart of SRILAC BIS with optical FA bus network with redundancy.

Figure 2: Whole system chart of machine protection for SRILAC operation. The SRILAC BIS is implemented in the central blue part, and the beam is stopped by the beam chopper by inputting the interlock signals from other systems.

#### **PASJ2021 TUP042**

Table 1: The PLC units and number of I/O signal points. The just numerical values are the number of installed I/Os. The numerical values in parentheses are the number of I/Os in use as of July 2021 for SRILAC operation.

|    | Main       | #1        | #2         | #3        | #4        | #5         | #6         | #7 |

|----|------------|-----------|------------|-----------|-----------|------------|------------|----|

| DI | 56<br>(36) | -         | 32<br>(29) | -         | -         | 32<br>(17) | 32<br>(10) | 0  |

| DO | 56<br>(8)  | 32<br>(1) | 32<br>(4)  | 32<br>(6) | 32<br>(0) | 32<br>(0)  | 32<br>(2)  | 0  |

| AI | 8 (1)      | 8<br>(1)  | 8<br>(8)   | 8<br>(0)  | 8<br>(0)  | 8<br>(0)   | 8<br>(0)   | 0  |

#### 3.5 高速 I/O

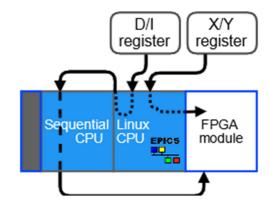

一般的に PLC は比較的遅い数 msec の応答速度でシステムを実現できる。一方で μsec オーダーの応答速度のシステムを実現するためには FPGA を選定する事がある[4]。 SRILAC 運転においてもキャビティの放電をトリガにビーム停止させるケースで、高速な応答速度が必要になると考えられる。 FA-M3 ベースな BIS で高速な応答速度を実現する手段として、フィールドプログラマブル高速 IO モジュール (F3DF01: FPIO モジュール) [11]を選定してロジックを実装した。 FPIO モジュールは Xilinx Spartan®-6 LX[12]の FPGA が内蔵されたモジュールであり、入力 24点、出力 24点を高速 I/O として持つ。シーケンス CPU モジュール側で走っているプログラムのスキャンタイムの影響を受けずに並列に処理させることが可能である。本システムではレジスタを介して FPIO

モジュールの各入力信号に対し有効/無効等の設定を行わせている。システムの概念図をFig. 3 に示す。

Figure 3: Accessing method to the FPGA module. Using D/I register, values are passed to the FPGA module. X/Y register of the FPGA module can also be accessed directly from the Linux CPU.

#### 3.6 上位システム

これら BIS への設定や情報表示、インターロック発報ログの取得等、上位システムとのコミュニケーションについてはセカンダリ CPU としてインストールされた Linux CPU 上で走る EPICS を経由して行われる。SRILAC BISの情報表示用 GUI パネルは CSS BOY を用いて構築されている (Fig. 4 参照)。また BIS 発報ログに関しては

Figure 4: Screen shot of the graphical user interface for SRILAC BIS.

caMonitor で Linux IOC からイベントドリブンに取得し、WebSocket で情報配信するシステムが運用されている。

# 4. システム性能

3.4 にて前述されている標準 I/O の応答速度を測定した。条件はサブユニット#6 の F3XD32-3F に 100 Hz の繰り返しでインターロック信号を入力し、メインユニットに接続したチョッパースイッチから出力がなされる間の時間を応答速度とした。結果としては平均 6 msec で動作した事を確認した。

また、3.5 にある高速 I/O についても測定を行った。メインユニットにインストールされた FPIO モジュールの入力に 100 Hz のインターロック信号を入力し、同様にチョッパースイッチから出力がなされる間の時間を応答速度とした。 結果は約 78 µsec であった。

# 5. サブシステム

#### 5.1 ソフトウェアインターロック

BIS にインターロック信号を入力するには配線やイベント時のトリガ信号の作成等それなりにコストがかかる。 SRILAC ビームコミッショニング中のインターロック取り込みの要求に迅速に対応できるシステムとして、ソフトウェアインターロックも実装されている。各 EPICS IOC の PV 値を CA 経由で F3RP71 に実装された EPICS Sequencerで取り込みさせ、1 秒以下の応答速度でインターロック出力させる事が可能である。出力されたインターロック信号は接点信号として SRILAC BIS に入力される。実際にはSRILAC ビームコミッショニング中、電磁石電源の電流値や RF 電圧のふらつき、また真空度の悪化を検知する目的で実装された。

#### 5.2 Curs-BIS

SRILAC ビームコミッショニング中 5.1 で前述したソフトウェアインターロックによって電磁石電源の電流値のふらつきを検知しインターロック出力を作成していた。一方でソフトウェアインターロックは簡便に実装できる反面、信頼性や応答性能は高くなく、また J-PARC では信号点数が際限なく増える恐れがある、という問題点も報告されている[13]。

RILAC 入射系以外の RIBF 運転ではビームパワーの増大に伴い、電磁石電源の電流値の変化を検知してビーム停止させるインターロックシステム(Beam Interlock System driven by change in current: Curs-BIS)[14]が運用されている。そこでソフトウェアインターロックに代わり Curs-BIS を RILAC 入射系の電磁石電源へ実装する計画をしている。2021 年 7 月現在、RILAC 入射系の電源 筐体 4 台が Curs-BIS に対応しており、今年中に全台数の電源を Curs-BIS に導入させる予定である。

## 6. まとめ

SRILAC 運転のためにマシンプロテクションシステムを構築した。システムの中心部分として SRILAC BIS を開発し、他システムからのインターロック出力を入力することで運用している。SRILAC BIS にインターロック出力が入力された後、予め設定されたロジックに基づきビーム

チョッパーとファラデーカップが駆動されて速やかにビーム停止することができる。応答時間は標準 I/O で約 6 msec だったため、PLC ベースのシステムとしての性能は出ている。また、従来 PLC ベースのシステムで難しかった 1 msec 以下の応答速度を実現するため、FPIO モジュールを導入、FPGA内部ロジックをシーケンス CPUとは別に開発をした。2020年1月に SRILAC ビームコミッショニングを終え、マシンプロテクションシステムは問題なく運用することができた。

# 謝辞

SRILAC用のマシンプロテクションシステムの構築にあたり、有益な討論、助言を戴いた Cosylab 社 Rok Hrovatin 氏に感謝します。

# 参考文献

- [1] T. Nagatomo *et al.*, "New 28-GHz Superconducting Electron Cyclotron Resonance Ion Source for Synthesizing Super-Heavy Elements with Z> 118", Proceedings of the 23th Int. Workshop on ECR Ion Sources, Catania, Italy, Sept. 10-14, 2018, pp. 53-57.

- [2] K. Yamada et al., "Construction of Superconducting Linac Booster for Heavy-Ion Linac at RIKEN Nishina Center", Proceedings of the 19th Int. Conf. on RF Superconductivity, Dresden, Germany, June 30-July 5, 2019, pp. 504-509.

- [3] M. Komiyama *et al.*, "Beam interlock system at RIKEN RI beam factory", Proceedings of the 2nd Annual Meeting of Particle Accelerator Society of Japan and the 30th Linear Accelerator Meeting in Japan, Tosu, Jul. 20-22, 2005, p.615.

- [4] R. Schmidt et al., "Machine Protection and Interlock Systems for Large Research Instruments", Proceedings of ICALEPCS2015, Melbourne, Australia, Oct. 17-23, 2015, pp. 537-542.

- [5] M. Komiyama et al., "Upgrading the Control System of RIKEN RI Beam Factory for New Injector", Proceedings of ICALEPCS2009, Kobe, Japan, Oct. 12-16, 2009, pp. 275-277.

- [6] M. Komiyama et al., "Recent Development of the RIKEN RI Beam Factory Control System", Proceedings of PCaPAC2018, Hsinchu, Taiwan, Oct. 16-19, 2018, pp. 66-68

- [7] A. Uchiyama et al., "Control System Renewal for Efficient Operation in RIKEN 18 GHz Electron Cyclotron Resonance Ion Source", Review of Scientific Instruments 87, 02A722 (2016).

- [8] https://github.com/EPICS-F3RP61

- [9] M. Komiyama et al., "Recent Update of the RIKEN RI Beam Factory Control System", Proceedings of ICALEPCS2017, Barcelona, Spain, Oct. 16-19, 2017, pp. 427-430.

- [10] General Specifications, "FA-M3 基本入出力モジュール" GS 34M06G01-01.

- [11] General Specifications, "F3DF01-0N フィールドプログラマブル高速 IO モジュール", GS 34M06H71-01-特 01.

- [12] https://japan.xilinx.com/products/silicon-devices/fpga/spartan-6.html

- [13] K. Sato et al., "Development and Operation of the EPICS-based Soft-MPS in J-PARC MR", Proceedings of the 16th Annual Meeting of Particle Accelerator Society of Japan July 31-August 3, 2019, Kyoto, Japan, pp.279-282.

- [14] K. Kumagai *et al.*, "Development of beam interlock system driven by change in current of the magnet", RIKEN Accel. Prog. Rep. 52 (2019), pp.115.