# SACLA と SPring-8 蓄積リングの高周波基準信号の同期システム その2

# SYNCHRONIZATION SYSTEM BETWEEN TWO MASTER OSCILLATORS OF SACLA AND SPRING-8 STORAGE RING 2

大島隆<sup>#, A, B)</sup>,細田直康 <sup>A, B)</sup>,前坂比呂和 <sup>B)</sup>

Takashi Ohshima <sup>#, A, B)</sup>,Naoyasu Hosoda<sup>A, B)</sup>,Hirokazu Maesaka<sup>B)</sup>

<sup>A)</sup> Japan Synchrotron Radiation Research Institute

<sup>B)</sup> RIKEN SPring-8 Center

#### Abstract

Preparation of a timing system to inject a beam from a linac of SACLA to the Storage Ring (SR) of SPring-8 is underway. One of the challenges is to synchronize two accelerators without degrading the performance of the XFEL operation of SACLA. We tested a prototype of a synchronization system by adjusting the timing of the master trigger signal of SACLA to the revolution timing of SR, and by applying FM modulation to the master oscillator of SACLA. We succeeded in synchronizing the timing between two signals (a 79 MHz signal which is one-third of 238 MHz of SACLA's timing reference frequency, and an 85 MHz signal which is one-sixth of 508.58MHz of SR's one) within 1.2 ps rms. But we also observed a phase slip in a PLL circuit of a laser used at pump and probe experiments at SACLA. A counter measure was tested which utilized that the timing of the 79 MHz signal relative to the 85 MHz signal changes -0.1 ns after one revolution period of the SR. The timing difference was minimized from 12 ns to 0.1 ns by waiting appropriate revolution count before generating the master trigger signal. On the other hand, this timing delay caused the deviation of the master trigger signal from the AC 60 Hz zero crossing timing, which lead to the beam kick by the heater current of the electron gun. We measured the effect of this timing deviation on the beam position and angle. We found the deviations were less than 3 μm and 0.2 μrad with a 0.2 ms delay from zero-cross timing, which were acceptable level. The injection test from SACLA to SR will be started in 2018 fiscal year.

#### 1. はじめに

SPring-8の次期計画 SPring-8-II [1]では入射ビームに 低エミッタンスが要求されるため、XFEL マシンである SACLA の線形加速器を入射器とする予定である。また、 今の SPring-8 蓄積リングにおいても SACLA からの入射 を先行して行う予定である。そのためには SACLA の線 形加速器と蓄積リング(SR)との2つの加速器のタイミング を入射時に数 ps の精度で同期させる必要がある。文献 [2]にて、同期の手法を提案し、原理検証の結果を示し た。そこに示した方法は以下の通りである。SACLA のタ イミング基準となるマスタートリガは、商用 60 Hz 信号と 79 MHz 信号との同期を取ったタイミングで発生させてい る。このトリガを SR の入射バケットの周回タイミングの 208 kHz 信号と同期させる。これにより、79 MHz の周期 である 12 ns を超えない同期を実現させる。残った時間 差は SACLA のマスターオシレータに FM 変調を加える ことにより抑制する。この方式に基づき、模擬入力信号を 用いた試験を行ったところ、1.2 ps rms のタイミング同期を 取ることができた。しかし、この試験の際に SACLA のポ ンプ・プローブ実験で使用される同期レーザーのPLL回 路に飛びが発生し、XFEL の実験に支障となることがわ かった。この原因は、FM変調の振幅が PLL 回路の許容 範囲を超えて大きかったためだと考えられる。

上記の問題を解決するために、16 ms の時間内に印加する FM 変調による最大時間調整幅を 12 ns からより小さい値に抑える工夫を検討した。その一つは、SACLA

# ohshima@spring8.or.jp

のタイミング基準信号 79 MHzとSR 周回信号との間のタイミング関係が、蓄積リングの周回時間を1回だけ待つと、-0.1 ns だけ変化することを使い、マスタートリガのタイミングを遅らせることでFM 変調振幅を抑制する方法である。本発表では上記タイミング同期方法の詳細、マスタートリガを AC ゼロクロスから遅らせることによる影響の評価、SACLA の線形加速器から SR へのビーム入射の今後の予定について報告する。

# 2. マスタートリガタイミングの調整方法

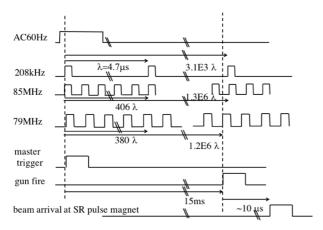

SACLA から SR への入射を行う際のタイミングチャー トの例を Figure 1 に示す。SACLA の線形加速器では、 AC 60 Hz、79 MHz に同期したマスタートリガを受けて、 クライストロンの高電圧電源の充電が開始される。この充 電の完了する 15 ms 後に電子銃がトリガされ、電子ビー ムが引き出される。約 400 m の線形加速器、約 200 m の アンジュレータビームラインをおよそ 2 μs の時間をかけて 電子ビームは通過し、ダンプに捨てられる。蓄積リングに 入射する場合には、線形加速器最下流で分岐して、さら に1 km ほどの輸送ビームラインを経て電子ビームは SR 入射部に運ばれる。電子銃のトリガから、SR 入射電磁石 に電子ビームが到達するまでにかかる時間は一定であ る。したがって、固定の遅延時間分を差し引いたタイミン グで周回信号を送り、それに同期したタイミングで SACLA のマスタートリガを発行すれば、狙ったタイミング で蓄積リングにビームを送ることができる。蓄積リング周 回信号と、マスタートリガの同期は、AC 60 Hz、周回信号、 79 MHz 信号を使ったフリップフロップ回路の出力で得ら れる。この時、周回信号とマスタートリガとの時間差は最

#### **PASJ2017 WEP066**

大 12 ns となる。この時間差は、要求されている数 ps 以内のタイミング誤差に比べて桁違いに大きい。そのため、何らかの方法で時間差を抑える必要がある。

Figure 1: Timing chart for injection from SACLA to SR.

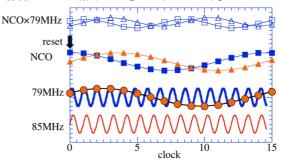

時間差を抑える際に、まず、その時間差を正確に計測 することが必要になる。その方法の1つとして、周回信号 の 406 倍の周波数 85 MHz をクロックとして、SACLA タ イミング基準 79 MHz を測定する方法を提案した[2]。こ の方法では、まず、85 MHz のクロックで動作する ADC に 79 MHz の信号を入力し、差周波の 5.4 MHz のデー タ列を得る。これと並行して、85 MHz をクロックとして 5.4 MHzの正弦波信号、余弦波信号を出力する Numerically Controlled Oscillator (NCO)を用意し、リセッ ト操作を、時間差を計測したいタイミングで行う。次に、 ADC のデータと上記 NCO の 2 信号との積 I および Q を 得る。この操作はデジタルダウンコンバージョンに相当し、 積のデータ列には 5.4 MHz の 2 倍波と、2つの信号の位 相差の情報を持つベースバンド信号が含まれる。低域 通過フィルタを通してベースバンド成分を抽出し、逆正 接の演算を行うことにより、位相を得ることができる。 79 MHz 信号、85 MHz 信号および NCO 信号との時間 関係の例を Figure 2 に示す。ここで、注意すべき点は、 ADC から得られる信号と NCO との位相差が 0 度である ことは、85 MHz と 79 MHz との位相差が常に 0 度である ことを示しているわけではなく、あるタイミングでリセット操 作を行なった NCO と同じタイミングで動作する状況に 持っていくことができた、ということのみを意味していると いう点である。85 MHzと79 MHzの位相差は時事刻々と 変化し続ける。ただ、NCO と同じタイミングで動作する信 号について、85 MHz 信号の周期の設定値倍だけ遅延 したタイミングでは、79 MHz の位相は一定の値を持ち、 そのタイミングでの遅延時間は一定値となる。

前節で示した方法で計測した時間差をもとに、タイミング差を抑制する方法について検討する。蓄積リングの目標としたバケット電子ビームを入射できるタイミングは、蓄積リングの周回時間ごとに発生する。これは、入射タイミングを周回時間の整数倍だけ遅延させても問題がないということを示している。そこで、リングを1周回った時間後に85 MHzと79 MHzの時間差がどれだけ変化するのかを求めてみる。周回時間は85 MHz の周期の整数倍で

あるので、スタートの時間が  $85~\mathrm{MHz}$  の位相  $0~\mathrm{g}$ であれば、1周回後も  $0~\mathrm{g}$ である。 $79~\mathrm{MHz}$  の信号について、 $1~\mathrm{g}$  周後に発生する時間差  $\mathrm{dt}$ , 位相差  $\Delta\phi$  は以下の式で表される。

$$dt = \left\{ \frac{1}{208 \text{ kHz}} - \frac{\text{int}\left(\frac{79 \text{ MHz}}{208 \text{ kHz}}\right)}{79 \text{ MHz}} \right\} \approx -0.1 \text{ns}$$

$\Delta \phi = 2\pi \times 79 \text{ MHz} \times dt = -2\pi \times 0.0086$

このことから、次の手順を踏むことで、 $85~\rm MHz$  と  $79~\rm MHz$  の時間差を  $0.1~\rm ns$  以内に抑えることが可能となる。

- AC 60 Hz のタイミングで NCO の reset を行い、位相差 Ø を検出する。

- 2. 得られた位相差 $\phi$ から待ち周回数 $n = \phi/\Delta \phi$ を計算する。

- 3. 得られた待ち周回数だけ待ったところでマスタート リガを出力する

残った 0.1 ns 以下の時間差の抑制は、文献[2]で示したように、SACLA の master oscillator に対して FM 変調を印加することで行う。この時の FM 変調の大きさは、0.1 ns / 15 ms ~ 7E-9 であり、12 ps を 15 ms で変調した場合に比べ2桁小さいものとなっている。

Figure 2: Timing relation of 79 MHz input signal, 85 MHz clock signal and NCO signals.

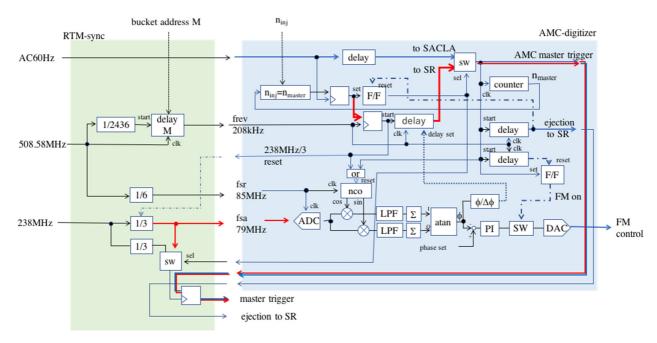

#### 3. MTCA.4 規格同期回路の製作

第2章で述べた方法を、MTCA.4 規格[3]のモジュールを使って確認した。Advanced Mezzanine Card (AMC) デジタイザとして、16-bit の分解能、125 Ms/s のサンプリング速度を持つ SIS-8300L を用い、デジタイザへの信号入力には新規に Rear Transition Module (RTM)を開発した。

デジタイザの FPGA には、Figure 3 右側に示す機能を持つ firmware を制作し実装した。 XFEL 実験の際には、AC 60 Hz 信号を固定の遅延時間だけ遅らせた信号をマスタートリガとして出力し、79 MHz クロックで再同期したのちに SACLA の加速ユニットに伝送する。 蓄積リングへの入射については、以下の手順を取る。 マスタートリガのカウント数を積算しているマスタートリガカウントがあらかじめ設定した SR 入射カウントに合致し、AC 60 Hz と周回信号が同期した時に、NCO をリセットし、この時の

Figure 3: Block diagram of timing synchronization system.

79 MHz 信号の位相を測定する。この位相から周回遅延量  $n = \phi/\Delta\phi$  を計算し、設定した遅延量になった時にマスタートリガを出力する。マスタートリガを出力したタイミングで再度 NCO をリセットし、79 MHz の位相を求める。この位相を元に SACLA のマスターオシレータを FM 変調することにより、位相差を目標値に保つ。

RTM の回路ブロック構成図を Figure 3 左側に示す。 SR の 508.58 MHz 基準信号を入力し、その 1/6 に分周した 85 MHz クロック信号、および 1/2436 に分周した 208 kHz 周回信号を AMC に送る。この時、周回信号には SR の目標とするバケットアドレスの番号 M に対応する遅延を I2C シリアル通信で設定する。また、SACLA の基準信号 238 MHz を 1/3 に分周した 79 MHz 信号を AMC に送る。 AMC から送られてくる AMC マスタートリガ信号を 79 MHz 信号で再同期し、SACLA の線形加速器の各ユニットに送る。

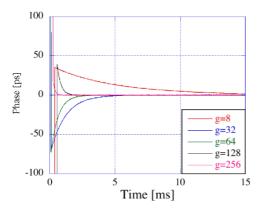

Figure 4: Example of the measured phase of 79 MHz signals with a test setup. The feedback gains were changed from 8 to 256.

シンセサイザーから出力される模擬信号を同期システムに入力して測定した位相読み取り波形の例を Figure 4に示す。PI 制御の利得を大きくすると制定時間が短くなる。利得を 64 に設定した場合、およそ 2 ms で位相は目標値に制定している。この状態で、14 ms から 15 ms までの位相平均値の 10 ショットのデータに対する標準偏差は 0.7 ps であった。この値は SR 入射のタイミング要求精度を満たしている。

# 4. SACLA のマスタートリガのタイミングずれ 許容量

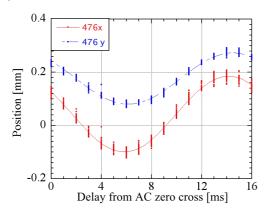

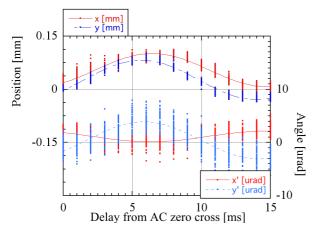

マスタートリガのタイミングは、AC 60 Hz 信号のゼロク ロスタイミングと同期させている。これは電子銃のカソード ヒータの電流が変更されたとしても、この電流が作る磁場 の変化によってビーム軌道に変化が与えられることを抑 制するためである。しかし、第2章で述べた方法では、 FM 変調の最大制御量が抑制される代わりに、マスタート リガのタイミングが上記のゼロクロスタイミングからズレるこ ととなる。 最大の遅延量は、79 MHz の 1 周期の 12 ns を 補正する場合で、0.6 ms となる。 そこで、 マスタートリガの タイミングを AC 60 Hz 信号のゼロクロスのタイミングから 1 ms ステップで変化させた場合の電子ビーム軌道変化 を、電子銃に近い 476 MHz ブースター空洞上流、およ び、BL3 アンジュレータビームライン上流部で確認した。 それぞれの位置でのビームの水平、垂直方向の位置の 変化を Figure 5, 6 に示す。 Figure 中では測定値を点で 示しており、そのデータを正弦波でフィットした結果を線 で示している。476 MHz 空洞上流では最大で水平に 0.15 mm、垂直に 0.10 mm の変化が見られた。この軌道 変化の影響は下流まで伝搬しており、BL3 での位置の 変化は最大で約 50 μm、角度の変化は水平 1 μrad,垂直 3.5 μrad であった。このことから、マスタートリガのタイミン

### **PASJ2017 WEP066**

グが 0.6 ms ずれた場合、輸送系のオプティクスにもよる が、SR 入射点で位置が  $10 \mu m$  程度、角度が  $0.8 \mu rad$  程度変化することが想定される。

この変化量を抑制するために、79 MHz との同期ではなく、238 MHz との同期に切り替えることが考えられる。 SR に入射する電子ビームのタイミングは、同期レーザーに合致している必要はない。これにより、タイミングのずれの最大値は 12 ns から 4.2 ns に抑制できる。79 MHz 信号は、238 MHz 信号を 1/3 に分周して作られるので、分周器を適切なタイミングでリセットすることでゼロクロスからのずれは 42 周回分に相当する 0.2 ms に抑制できる。この場合、位置および角度の変化は約 3 μm、および 0.2 μrad に抑えられ、許容値内に収まると期待される。

Figure 5: Horizontal and vertical beam positions at 476 MHz cavity entrance as a function of delay from AC 60 Hz zero cross timing.

Figure 6: Beam positions and angles at the beamline BL3-0 as a function of delay from AC 60 Hz zero cross timing.

# 5. まとめと今後

SACLA の線形加速器を SR の入射器とする運転で必要となる、タイミング同期回路の改善を行った。マスタートリガ信号のタイミングを、蓄積リングの周回周波数の整数倍だけ遅延することにより、タイミング差を 0.1 ns 以下に抑えることができた。しかし、その代償として AC 60 Hz とマスタートリガ信号のタイミングに最大 0.2 ms のずれが生じる。そこで、このタイミングのズレが電子ビームに与える影響の測定を行なった。その結果、マスタートリガの ACゼロクロスからのタイミングズレが 0.2 ms の場合に、BL3アンジュレータ上流部で電子ビームの位置および角度の変化が約 3 μm、および 0.2 μrad に相当することがわかった。SR 入射部においても電子ビームの位置、角度の変動がこれと同等であるとすると、これらの値は許容できる範囲だと考えられる。

SACLA 線形加速器からリングへのビーム入射に向けた準備は、2018年度に試験的入射の予定に向けて着々と進められつつある。SACLA のマスターオシレータ室と蓄積リングの RF ステーションとの間を結ぶ光ファイバの敷設は昨年度完了している。蓄積リングから 508.58 MHz基準信号を伝送するために使用する光送・受信機の位相雑音は 10 Hz から 10 MHz のオフセット周波数の範囲で 100 fs 以下の増加に抑えられていて、要求仕様を満たすことが確認された。SACLA の線形加速器の RF パラメータを SR 入射のショットに対して変更する制御システムの開発も期限に間に合うように進められつつある。

# 謝辞

同期試験を行うにあたって、AMC の FPGA に実装する firmware 制作に協力いただいた三菱電機特機システム[4]の岩城氏、漁師氏、同期 RTM の製作に協力いただいたキャンドックスシステムズ[5]の仙石氏、埜下氏、および、様々な段階で的確な助言を与えてくださった播磨理研放射光研究センターの方々に感謝の意を示す。

# 参考文献

- [1] SPring-8 Project Facility Design (1991).

- [2] T. Ohshima *et al.*, "SACLA & SPring-8 蓄積リングの高周波基準信号の同期システム", Proc. of 13th Annual Meeting of Particle Accelerator Society of Japan, (2016) pp.832-835.

- [3] http://mtca.desy.de

- [4] http://melos.co.jp

- [5] http://www.candox.co.jp