# KEK-PF 高速パルスキッカーのための SiC 半導体スイッチを用いた 高速パルス電源の開発と高繰り返し試験

# HIGH REPETITION TESTS OF A PROTOTYPE PULSED POWER SUPPLY USING SIC-MOSFETS FOR A FAST KICKER SYSTEM IN KEK-PF

篠原智史 \*,A), 満田史織 A), 内藤大地 A), 奥田貴史 B), 中村孝 B)

Satoshi Shinohara \*,A), Chikaori Mitsuda A), Daichi Naito A), Takafumi Okuda B), Takashi Nakamura B)

A) High energy accelerator research organization (KEK)

B) NexFi Technology

## Abstract

We are developing a pulsed power supply using SiC-MOSFETs for a fast kicker system in the KEK-PF 2.5 GeV storage ring. The kicker system requires the pulsed power supply to generate half-sinusoidal pulses with a large peak current of 500 A within a 1% uncertainty, a short pulse width of 200 ns, and a high repetition rate of 800 kHz. In the previous prototype development, we found that the prototype could generate the required pulses at a low repetition rate of 10 Hz. To generate required pulses at higher repetition rates, we started to develop a new prototype. The challenges in the new development were to shorten the charging time of resonant capacitors and to ensure adequate thermal management. Additionally, the film capacitors used in the previous prototype were found to deteriorate as the number of repetitions increased. In the new prototype development, we adopted an energy recovery circuit, enabling rapid charging and improved heat dissipation, and vacuum capacitors that did not degrade with a large number of repetitions. In this report, we describe the design of the new prototype and the evaluation results of the peak current during tests at repetition rates exceeding 100 kHz.

# 1. はじめに

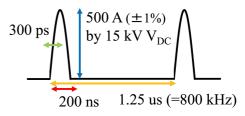

放射光源加速器 KEK-PF 2.5 GeV リングではカムシャ フトバンチシステム [1,2] の導入を計画しており、そ のための高速キッカーと高速パルス電源が必要である。 特にパルス電源においては Fig. 1 に示すような大電流 (500 A) 短パルス (200 ns 幅) を高繰り返し (800 kHz) で 駆動可能な電源が必要であり、カムシャフトバンチシ ステム導入の鍵となっている。そこで KEK-PF では高 繰り返しで短パルス出力可能な半導体スイッチング素 子 SiC-MOSFET に注目し、パルス電源の開発を行って きた。試作初号機開発では、1.2 kV SiC-MOSFET 16 直 列で構成されるスイッチングモジュールを組み込んだ パルス電源試作機の初号機開発を行い、実験室環境にて 10 Hz の低繰り返しではあるが、要求安定度を満たす出 力が可能なことを確かめた [3-5]。一方で初号機は高繰 り返し運用に伴う発熱の対処やパルス電源の充電能力が 十分でなく 100 kHz を超えるような高繰り返し運用はで きなかった。またパルス出力に重要な充放電コンデンサ も繰り返し数が増大すると容量が劣化するものがあると 判明したため、高繰り返し運用に十分耐えうるデバイス の開発も必要となった。そこで今回、投入電力を低減し 発熱も軽減可能なエネルギー回生回路の導入と高繰り返 し運用可能な真空コンデンサバンクを搭載した試作次号 機開発を行った。本報告では、今回開発した高繰り返し 対応パルス電源の設計と、100 kHz を超える高繰り返し 試験時のパルス電流ピーク電流値の評価結果ついて報告 する。

Figure 1: Schematic of required half sinusoidal wave pulses.

# 2. 高繰り返し駆動可能なパルス電源の開発

#### 2.1 高繰り返しパルス電源設計概要

本章では今回開発した高繰り返し可能な半導体パルス 電源の設計概要と開発の様子について述べる。

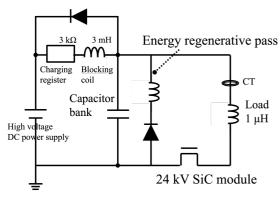

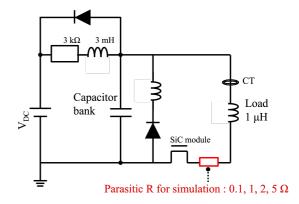

Figure 2 に開発した高繰り返しパルス電源試験機の回路図概略を示す。回路方式はインダクタンス負荷と共振コンデンサを用いた LC 共振回路を採用した。この回路方式はこれまでに開発してきた SiC-MOSFET を用いた半導体パルス電源 [3–5] にも採用しており、数十 Hz 程度の低繰り返しではあるがピーク電流値が 500 A を超えるパルス電流を安定度 0.2% 以下と目標安定度以下で出力できることが分かっており、今回の開発でもこれまでに開発した電源回路を拡張する形で開発を行なった。Figure 2 に示したパルス電源回路は大きく 2 つのパートに分かれており、一つは高圧 DC 電源や充電抵抗、突

<sup>\*</sup> sshino@post.kek.jp

Figure 2: Schematic of the circuit of a prototype for high repetition tests.

入電流抑制コイルを有する回路部 (DC 部)、もう一つは 充放電用のコンデンサやインダクタンス負荷、スイッチ (SW)を有する回路部 (パルサー部)に分かれる。回路の 基本動作としては、まずスイッチ (SW)オフ状態で高圧 DC 電源から DC 部を介して充放電用コンデンサへ充電 され定常状態へと至る。その後、SW がオン状態になる とコンデンサに蓄積された電荷がパルサー部へ流入し始 める。この時、キッカーマグネットを模擬したインダク タンス負荷とコンデンサで LC 共振を起こし、正弦波を 生成する。適切なタイミングで SW を再びオフ状態にす ることで、再びコンデンサへの充電が始まり、定常状態 へと至る。この SW 動作を繰り返すことで、インダクタ ンス負荷へパルス電流を生成する。

100 kHz を超える高繰り返し駆動可能なパルス電源の 回路設計にあたり、回路上の課題は大きく二つある。一 つは繰り返しの時間間隔内に充電が完了することであ り、例えば 100 kHz 繰り返しであれば 10 μs 以内に充電 が完了する必要がある。繰り返しの時間間隔内で充電を 終えないと充電電圧が設定値よりも低くなり設定通りの パルス電流ピーク電流値を出力することができない。も う一つの課題は、高圧 DC 電源による投入電力を減らす ことである。目標であるピーク電流値 500 A 繰り返し 800 kHz の出力時には抵抗負荷で 200 kW 相当の出力と なるため、この電力を高圧 DC 電源で投入すると電源規 模が大きくなりすぎるため投入電力を減らすような工夫 が必要である。これら二つの課題を同時に解決するため 今回開発するパルス電源には Fig. 2 に示したエネルギー 回生経路を導入している。エネルギー回生回路を導入す ることで SW オン時に放電したエネルギーをパルサー部 で消費する前にエネルギー回生回路を通して充放電コン デンサへ再び充電することが可能である。エネルギー回 生による充電時間は、エネルギー回生回路にインダクタ ンス負荷と同程度のインダクタンス値をもつコイルを設 置することで出力パルス幅と同程度の時間(数 100 ns)で 充電が行えるため 100 kHz を超える繰り返しに対応でき るようになる。また高圧 DC 電源による投入電力もエネ ルギー回生中に消費した電力分だけ補えば良いので投入 電力の削減も行える。エネルギー回生の効率が 90% で あれば、投入電力は 200 kW から 20 kW となるため十分 実現が可能な電源規模となる。

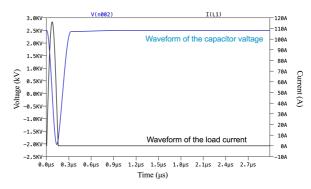

Figure 3 に LTSpice [6] シミュレーションによるイン

ダクタンス負荷に流れる電流波形とコンデンサの充電電圧波形を示す。電圧  $2.5~\rm kV$  印加でパルス電流  $100~\rm A$ 、パルス幅  $160~\rm ns$  のパルス電流を出力できており、電圧  $12.5~\rm kV$  印加では目標のピーク電流値  $500~\rm A$  も可能な回路設計にできた。また、コンデンサの充電電圧も  $10~\rm \mu s$  以内に回復しており、 $100~\rm kHz$  を超える繰り返し出力が可能な設計となった。

Figure 3: Simulated waveforms of the voltage of the charging/discharging capacitor (blue line) and the pulsed current of the load (black line).

#### 2.2 高繰り返し試験機の開発

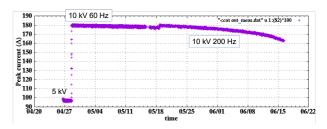

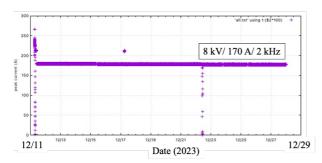

設計した回路の元で実際に高繰り返し対応のパルス電源開発を行った。デバイス開発の課題としては高繰り返し駆動に耐えうるコンデンサの開発がある。Figure 4 に示すのは、これまでの開発で用いていた高耐圧フィルムコンデンサを搭載したパルス電源の長期出力試験の様子である。パルス電流ピーク電流値の時間変化を示した図だが、ピーク電流値が次第に減少していることが分かる。原因としては、長期試験では6億回の高電圧スイッチングを行ったが、その間に高電圧スイッチングに伴うコンデンサ容量が劣化し出力ピーク電流値が減少したと考えられる。実際に、長期試験終了後にコンデンサ容量を測定すると容量は25%減少しており考察を裏付けるものとなった。このように高繰り返し電源の開発にあたっては容量劣化を起こさないコンデンサの開発が課題であった。

Figure 4: Long-term test of a pulsed power supply with film capacitors.

そこで今回の開発では真空コンデンサを用いたコンデンサバンクを導入を計画した。真空コンデンサは電極間を真空にしたコンデンサで真空の絶縁により高電圧でも使用でき、誘電体を用いないため誘電体損失がなく大電

#### **PASJ2024 WEP060**

流、繰り返しに強いという特徴がある。一方で、誘電体 を用いないため容量は大きくできず (最大 1 nF 程度) 大 容量の用途には適用できないというデメリットがある。 ただし、今回の開発するパルス電源に必要なコンデンサ 容量は 1-2 nF であるためデメリットとならずに適用可 能である。コンデンサバンクの開発にあたっては、目的 のパルス電源開発には高繰り返し駆動可能なコンデンサ バンクの開発は必須であったため、電源開発初期から真 空コンデンサメーカー (明電舎) と協力し開発を進めるよ うにした。Figure 5 に示すのは、開発した真空コンデン サバンクを搭載したパルス電源の長期出力試験の様子で ある。真空コンデンサ搭載機の長期試験では27億回の 高電圧スイッチングを行い、フィルムコンデンサ搭載機 の 4 倍以上のスイッチング動作を行ったが、ピーク電流 値の減少なくパルス出力を行えた。このように高繰り返 しに耐えうるコンデンサバンクの適用に成功した。

Figure 5: Long-term test of a pulsed power supply with vacuum capacitors.

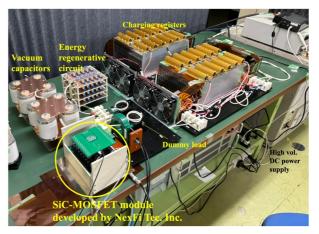

Figure 6 に開発した高繰り返し試験機の様子を示す。 試験機開発にあたり、まずは高繰り返し動作の課題発見 のため、パルス出力のピーク電流値は 100 A 程度に抑え て繰り返しが 100 kHz を超えて運用できるようデバイス 定格を設定した。使用スイッチングモジュール (SWM) は(株)ネクスファイテクノロジー製であり[7-9]、1.2kV 耐電圧の SiC-MOSFET を 20 直列に接続し(並列数は 1)、一つのモジュールを構成している。MOSFET のオ ン/オフに必要なゲート信号は一度光信号に変換するこ とで絶縁しており、またそれに必要な電力も無線電力伝 送によって絶縁しつつ供給している。SWM の大きさは 20 cm 角程度と小型ながら耐電圧は 24 kV と高耐電圧な モジュールとなっている。また、前試作機搭載の SWM は繰り返し周波数は最大 200 kHz であったが、放熱設計 を改善し水冷ヒートシンクにマウントすることで繰り返 し周波数が 400 kHz までのスイッチングが可能となっ た。コンデンサバンクは先述の真空コンデンサを使用し ており、250 pF のコンデンサ (SCF-352.5H65C; 明電舎) を4並列したものを1モジュールとし、モジュールを2 並列で運用して全体で 2nF とした。コンデンサバンクの 耐電圧は 21 kV であり、許容電流も 620 Arms と最終出 力目標の充放電にも耐えうるデバイスとなっている。そ の他、充電抵抗バンクはメタルクラッド抵抗を空冷ヒー トシンクにマウントして運用し、1.8kW まで入力可能で ピーク電流値 100 A のパルス電流を 400 kHz で駆動し ても運用できるようになっている。また回生経路に用い るダイオードバンクも 1.2 kV SiC-ショットキーバリア

ダイオード (SBD) を 20 直列 4 並列で構成されており、全体で  $24 \, \mathrm{kV}$  耐圧で  $500 \, \mathrm{A}$  の連続パルス運転が可能なようになっている。パルス電源に投入する電力は高圧 DC 電源によって行うが、将来的な定格向上や負荷調整、接地方法の裕度を持たせるため特別に開発した高圧 DC 電源 ( $12 \, \mathrm{kV}$ ,  $1.5 \, \mathrm{A}$ ; エイチ・エス・エレクトリック製) を用いて試験を行うこととした。

Figure 6: Prototype pulsed power supply for the high repetition rate tests..

# 3. 高繰り返しパルス電源出力結果

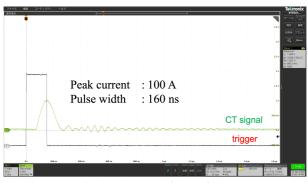

#### 3.1 単パルス出力試験

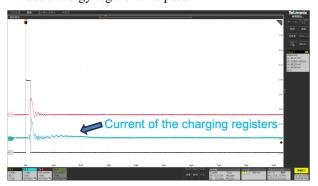

開発した試験機を用いてパルス電源の動作試験を実施した。Figure 7 に 2.3 kV の電圧を印加時にトリガー信号を単発で投入したシングルショットの波形を示す。パルス電流波形は CT (ピアソン社製, MODEL 110) により測定し、オシロスコープ (テクトロニクス社製のMSO64) にて波形を取得した。2.3 kV 印加時でピーク電流は 100 A, パルス幅 160 ns とピーク電流値とパルス幅ともに設計通りの正弦半波出力に成功した。正弦半波の後半にはリンギングが残存しているが、これは SiC SWM や SBD の浮遊容量によるものと考えられる。このリンギングはスナバ回路の導入により素早く収束させることができると実験により分かっており、今後スナバ回路の定数調整を実施する予定である。

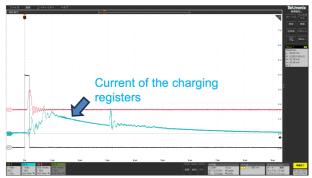

Figure 8,9 は DC 部充電抵抗に流れる電流波形の様子を示している。回生経路の有無で充電抵抗に流れる電流ピーク値が 1/10 以下に減っていることが分かり、エネルギー回生回路が十分に機能していると判明した。

### 3.2 高繰り返し試験結果

本節では、高繰り返し試験時のパルス出力ピーク電流 値評価結果と高繰り返し試験時に判明した課題について 述べる。

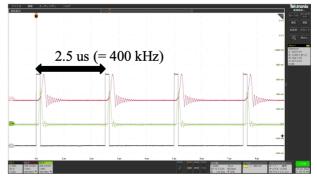

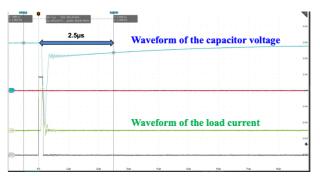

高繰り返し試験の実施にあたり機器発熱による故障が 懸念されたため、まずは印加電圧は 1.2 kV に抑えピー ク電流値は 50 A と低い状況から実験をはじめ、徐々に 繰り返しを上げて試験を行なった。Figure 10 にピーク 電流値 50 A 試験時の 400 kHz 繰り返し動作時の出力の 様子を示す。パルス出力間隔は 2.5 us であり、400 kHz

Figure 7: Single-shot waveform of the prototype.

Figure 8: Waveform of the current of the charging registers without a energy regenerative pass.

Figure 9: Waveform of the current of the charging registers with a energy regenerative pass.

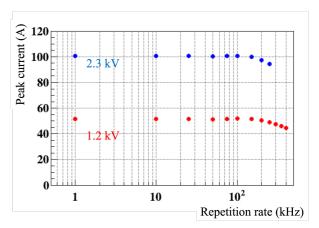

の高繰り返し出力に成功していることが分かる。一方でピーク電流値は低繰り返し時は 51.5 A だったのにも関わらず、400 kHz 駆動時には 44.7 A と 13% 低下していることが分かった。Figure 11 にピーク電流値と繰り返し周波数の関係を示す。図の各繰り返し周波数の点においては、50 波形を取得しピーク電流値の平均値を代表点として描画している。また、各点におけるピーク電流値分布の標準偏差をその点における誤差としている。ピーク電流値分布の標準偏差は 0.2 A 程度と小さく抑えるのでおり、パルス出力の安定度(ピーク電流値に対するあったが、Fig. 11 からも明らかなように繰り返し周波数を上げると 100 kHz を超える領域でピーク電流値が減少していく様子が見られている。印加電圧を 2.3 kV に上げてピーク電流値が 100 A となる試験も同様に実施したが、

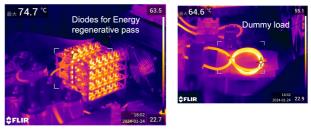

250 kHz 繰り返し時にはピーク電流値が 6% 減少する様子を確認した。またピーク電流値 100 A 試験の際、回路素子の発熱が Fig. 12 に示すように大きく 250 kHz までにとどめた試験とした。

繰り返し周波数の増加によりパルス出力ピーク電流値 の減少が見られたため、原因の調査を行った。高繰り返 し時にピーク電流値が減少していることから、充電電圧 が設定電圧に対して追いついていないことが疑われたた め充電電圧波形を測定した。トリガーを単発で入れてス

Figure 10: Waveforms of the pulsed current in the high repetition rate tests.

Figure 11: Peak current of the output pulsed current as a function of a repetition rate. The red and blue dots show peak currents tested at 1.2 kV and 2.4 kV supplied voltages, respectively.

Figure 12: Thermal distribution acquired by thermography (E54; FLIR). The left and right figure show the thermal distribution of the diode bank of the energy regenerative pass and dummy load, respectively.

# PASJ2024 WEP060

イッチングさせた際の測定結果を Fig. 13 に示す。電圧は高電圧差動プローブ (THDP0100) を用いた。電圧測定の結果から分かる通り、コンデンサ電圧は定常状態に回復するまでに 10 us 以上の時間がかかっている。このため 100 kHz を超える繰り返し動作時には充電が間に合わずピーク電流値が減少していったと思われる。シミュレーションではエネルギー回生の効果により 300 ns 以内に急峻に回復することを目論んでいたが、データではエネルギー回生の効果は見えるもののエネルギー回生による充電電圧の回復は 7 割程度に収まっていることが判明した。

Figure 13: Measured waveforms of the voltage of the charging/discharging capacitor (blue line) and the pulsed current of the load (green line).

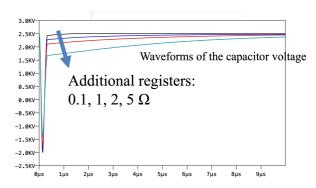

エネルギー回生効率が悪く充電の追従性が遅い原因 についてシミュレーションにより更なる検討を行った。 現実の回路ではエネルギー回生の効率が良くないこと から、パルサー部に考慮しきれていない電力消費源があ ると考え、Fig. 14 に示すようにシミュレーション上で 抵抗を疑似的に追加し充電電圧波形の変化を調査した。 Figure 15 にシミュレーションで得られたコンデンサ充 電電圧波形を示す。パルサー部上の抵抗値が増えていく とデータの充電電圧波形に近づいていくことが分かる。 SiC-MOSFET SWM の直列抵抗が 1 Ω 程度あることは 見込んでいたが、シミュレーションでは  $1 \Omega$  を大きく 超える抵抗の存在を示唆している。考えられる原因とし ては、出力正弦半波のパルスや後段のリンギングの周波 数が 10 MHz 程度と低くない周波数領域なため、回路 構成要素の表皮抵抗が増加してしまったためと考えてい る。本試験では抵抗が増加している具体的な箇所は特定 できておらず、回路構成要素に限らずモジュール間を接 続している配線も含めて今後調査を行い対策する予定で ある。

### 4. まとめ

KEK-PFではカムシャフトバンチシステム導入のための SiC-MOSFET を用いた半導体パルス電源の開発を進めている。パルス電源試作初号機は数十 Hz の低繰り返しで大電流短パルスの出力に成功しており、次のステップとして今回は高繰り返し可能な半導体パルス電源の開発を進めた。高繰り返し時の回路設計上の課題であった投入電力の低減と高速充電をエネルギー回生回路の導入によって改善し、また高繰り返しに耐えうるコンデンサバンクに真空コンデンサを導入することで高繰り返し時

Figure 14: Schematic view of the circuit for adding parasitic registers in the simulation.

Figure 15: Simulated waveforms of charging/discharging capacitor voltages at various parasitic resistors.

のデバイス上の課題も解決した。回生回路と真空コンデンサを導入したパルス電源を開発し、短パルス出力では2.3 kV の電圧印加時にピーク電流値100 A でパルス幅が160 ns と設計通りの出力に成功した。100 kHz を超える高繰り返し試験も実施し、印加電圧を1.2 kV に抑え出力パルスのピーク電流値を50 A に抑えた試験では400 kHz で故障なく駆動することに成功した。一方で、繰り返し周波数を上げていくとパルス出力のピーク電流値が減少していく様子が見られた。これはコンデンサの充電が設計通りに回復していないためであり、その原因は回路構成要素の表皮抵抗増大がエネルギー回生を阻害したため起きたと考えられる。今後、表皮抵抗が増大している箇所を特定し、より現実を反映したシミュレーションで設計を行なった上、目標の大電流高速高繰り返しの全てを両立する半導体パルス電源開発を目指す。

### 謝辞

本研究は JST A-STEP Grant Number JPMJTR201A, Japan の支援を受けたものです。

# 参考文献

[1] C. Sun, G. Portmann, M. Hertlein, J. Kirz, and D. S. Robin, "Pseudo-single-bunch with adjustable frequency: A new operation mode for synchrotron light sources," *Phys. Rev. Lett.*, vol. 109, p. 264801, Dec 2012.

- [2] C. Sun, D. S. Robin, C. Steier, and G. Portmann, "Characterization of pseudosingle bunch kick-and-cancel operational mode," *Phys. Rev. ST Accel. Beams*, vol. 18, p. 120702, Dec 2015.

- [3] S. Shinohara *et al.*, "Development of a Prototype Pulsed Power Supply using SiC-MOSFETs for a Fast Kicker System in KEK-PF," *JACoW*, vol. IPAC2023, p. THPA168, 2023.

- [4] S. Shinohara et al. in Proceedings of 19th Annual Meeting of the Particle Accelerator Society of Japan, pp. 1010–1014, 2022

- [5] S. Shinohara et al. in Proceedings of 20th Annual Meeting of

- the Particle Accelerator Society of Japan, pp. 863-867, 2023.

- [6] Analog Devices, Inc., https://www.analog.com

- [7] NexFi Technology Inc., https://www.nexfi-tech.com

- [8] T. Nakamura *et al.*, "Application of sic power devices to ultrahigh voltage equipment," in 2022 IEEE CPMT Symposium Japan (ICSJ), pp. 146–149, 2022.

- [9] T. Okuda *et al.*, "A 5-kV pulse generator with a 100-kV/μs slew rate based on series-connected 1700-V SiC MOSFETs for electrical insulation tests," *Review of Scientific Instruments*, vol. 92, p. 114705, 11 2021.